전공정

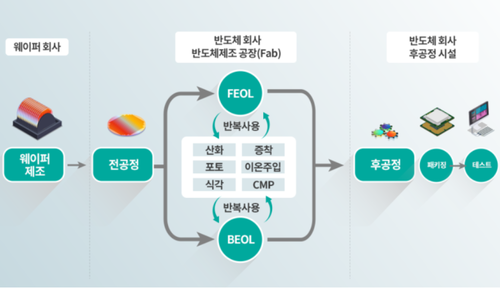

전공정(前工程, Front-end Process)은 웨이퍼 위에 반도체 디바이스(소자) 및 회로를 형성하는 단계이다. 이 작업이 선행되어야 후공정이 진행될 수 있다. 전체 단계를 FEOL(Front-End Of Line)이라고도 부른다.

전공정은 다시 Front-end of Line(FEOL) 공정과 Back-end of Line(BEOL) 로 나누어진다. 이 단계가 설계 기간의 대부분을 차지하기 때문에 대체로 '반도체 공정'이라고 하면 전공정을 의미하게 된다.

전공정은 8대 공정 중 산화공정, 포토공정, 식각공정, 증착 & 이온주입 공정, 금속배선 공정을 이용하여 진행된다.

목차

상세[편집]

전공정에 들어가기 전에 반도체 메이커가 필요로 하는 것이 있다. 크게 2 가지로 웨이퍼와 포토마스크이다. 실리콘(Si)의 단결정을 만들고 실리콘 단결정을 일정한 두께로 절단하여 웨이퍼를 만드는데 국내에서 LG 실트론과 MEMC 코리아에서 웨이퍼를 제조하고 있다. 웨이퍼의 원재료로 실리콘을 많이 사용하는 이유는 실리콘은 모래에서 추출할 수 있어 구하기 쉽고 독성이 없어 환경 친화적이기 때문이다. 또한 실리콘 웨이퍼는 넓은 에너지 밴드를 가지고 있어 비교적 고온에서도 소자가 동작할 수 있는 장점이 있기도 하다.

포토마스크는 웨이퍼 위에 이식할 설계 패턴을 웨이퍼에 전사하기 위하여 필요한 재료로서 피케이엘과 듀폰 포토마스크 코리아에서 생산하고 있다.

전공정은 기판공정과 배선공정으로 분류한다.

반도체 제조 업체는 웨이퍼와 마스크를 구입하여 전공정에 들어가는데 전공정은 크게 두가지 형태로 분류할 수 있다. 첫째는 웨이퍼 표면위에 산화, 확산등 여러 가공을 하는 기판 공정과, 둘째는 웨이퍼 표면에 배선을 형성하는 배선공정으로 나눌 수 있다.

반도체 제조공정에서는 먼저 기판공정이 시작되고 후에 배선공정을 진행하는데, 이 두가지 공정을 수행하기 위해서는 여러가지 웨이퍼 프로세스 기술이 필요하다. 크게 리소그래피 공정, 세정공정, 열처리공정, 불순물 도입공정, 막형성공정, 평탄화공정 등의 공정 기술이 사용된다.

- 세정공정

리소그래피 공정은 PR(감광액) 도포, 베이킹, 노광, 현상, 에칭, PR 제거등으로 나눌 수 있는데 각 공정 사이사이 반드시 세정 공정이 필요하다. 말 그대로 웨이퍼 표면 위에 남아있는 산화물 찌꺼기나 파티클을 정화하는 공정으로 회로 선폭이 미세화되어 고집적화 될수록 중요성이 커지고 있는 공정이다. 반도체 공정에서 가장 많이 사용되는 공정이기도 하다. 세정 방법으로는 크게 두가지가 사용된다.

첫번째 방법은 화학 약품(케미칼)으로 세정하는 Wet 세정방법과 반응성가스 내지 플라즈마를 이용하여 표면의 오염을 세정하는 Dry 세정방법이 있다. 현재 주로 쓰이고 있는 세정방법은 Wet 세정방법으로 세정 후의 폐수처리등 환경 문제점이 대두되고 있으나 Dry 방법보다 오염물 및 파티클 제거 능력이 우수하기 때문에 보편적으로 사용된다.

국내에서 세정 장비를 생산하는 대표적인 업체는 한국 DNS와 케이씨텍이 있다.

- 열처리공정

반도체 공정에서 고온 열처리 공정은 많이 사용되고 있고 열처리의 목적은 크게 세가지 정도를 꼽을 수 있다.

첫째는 산화공정으로서 산화막(SiO2)을 형성하는 공정으로 이 산화막은 절연막의 역할을 한다. 둘째는 확산공정으로서 불순물 원자를 열적으로 확산시켜 PN 접합을 형성하는데에 이용된다. 세번째는 어닐(Anneal)공정으로 쉽게 말해 가열하여 서서히 식히는 처리 방식으로 이해하면 된다. 어닐 공정은 주로 전기특성/계면특성 향상, 결함제거, 막질개선등 웨이퍼 특성을 안정화하는 목적을 지니고 있다. 이러한 열처리 공정을 처리하기 위해서는 장비가 필요한데 Furnace(확산로) 나 RTP(Rapid Thermal Processor)가 사용된다. Furnace 는 장시간 열처리하는데 적합하고, 웨이퍼의 온도를 안정하게 유지시키고 단위 시간당 처리량이 높은 장점이 있다.

RTP 는 단시간에 가열하여 온도를 상승시킬 수 있는 것이 최대 장점으로 여겨진다. 국내 장비 생산업체로는 장외업체인 코닉시스템이 있다.

- 불순물(이온)주입공정

불순물 주입 공정은 과거에는 열로 확산하는 방법을 사용하였으나 현재는 이온 주입법을 많이 사용하고 있다. 이온 주입법은 원하는 불순물을 가스상태로 만든 후 이온을 빼내어 가속화시켜 웨이퍼 기판에 주입한다. 불순물을 주입하는 것은 웨이퍼의 원하는 전기적 특성을 만들어주기 위한 것이다. 이온주입기(Ion Implanter)를 생산하는 국내 업체는 없으며, 전적으로 수입에 의존하고 있다.

- 박막형성 공정

박막형성은 반도체 제조 공정중에 방법 및 용도가 다양하게 이용되고 있으며 이에 따라 박막형성 장비도 다양하다. 박막형성 기술은 형성된 막이 디바이스의 특성 및 신뢰성에 큰 영향을주는 관계로 상당히 중요한 기술로서 그 위치를 차지하고 있다. 박막의 종류는 상당히 많은데 재료의 성질에 따라 대개 절연막, 금속막, Epi-taxial 이나 Poly-silicon 막등이 있으며 박막을 형성하는 방법에는 대표적으로 CVD(Chemical Vapor Deposition)방법, PVD(Physical VaporDeposition)방법이 있다.

CVD 법은 화학적 반응을 이용하여 박막을 형성하는 것으로 온도와 압력 등이 중요한 요소로 작용한다. 주로 Epi-taxial 성장, 폴리실리콘 막, 금속간의 절연막을 형성할 때에 사용된다. PVD 법은 Sputtering(에너지를 가진 입자가 target 에 충돌해 원자가 방출되는 현상)과 같은 물리적 방법을 응용한 것이다. 박막형성 장비는 전공정 장비 전체 시장의 15%를 차지할 만큼 시장 규모가 크다.

국내 대표적인 업체로는 주성엔지니어링을 들 수 있다.

- 평탄화 공정

웨이퍼의 표면을 평탄하게 연마하는 공정으로 반도체 제조공정이 고집적화되고 회로 선폭이 미세화됨에 따라 디바이스 소자의 배선 단절 현상이 발생하지 않도록 하기 위해 필수적으로 실시되는 공정이다. 평탄화 방법에는 몇가지가 있으나 가장 일반적으로 사용되는 방법은 CMP(Chemical Mechanical Planarization) 방법이다. 간단히 말하면 웨이퍼를 회전하는 탄성 패드(Pad) 사이에 화학액인 슬러리(Slurry)를 뿌려 웨이퍼 표면을 연마하는 기술이다. CMP 장비를 생산하는 국내 업체는 아직 없어 수입에 전적으로 의존하고 있다.

- 리소그래피 공정

리소그래피 공정은 전공정의 핵심이고 관련 장비 시장 규모가 가장 크다. 한편, 향후 반도체의 고집적화 성공 여부를 결정짓는 공정이기도 하다. 이 공정은 여러 단계의 공정들로 다시 세분화 되며 세정공정과 같이 각 공정들이 계속 반복되어 공정수가 제일 많다. 리소그래피 공정은 포토마스크 기판에 그려진 회로 패턴을 웨이퍼 위에 전사하는 것으로 세분화 해보면 크게 PR(감광액) 도포 -> 소프트 Bake -> 정렬 -> 회로 패턴 노광 -> PR 현상 -> 하드 Bake ->에칭(식각) -> PR 제거 -> 세정 등으로 나눌 수 있다.

간단히 공정을 설명하면, 웨이퍼 위에 도포된 PR 에 포토마스크를 통과한 빛이 투과되면 감광액이 변화된다. 그 다음 현상액을 통하여 현상한 다음 감광액을 건조시키는 하드 베이크를 거쳐 원하는 패턴을 형성하기 위해 불필요한 부분을 깎아낸 다음 PR 을 웨이퍼에서 제거하여 최종적으로 세정처리를 거친다.

리소그래피 공정 주요 장비로는 트랙장비, 노광장비인 스테퍼(Stepper), 에칭장비인 Etcher, PR제거장비인 Asher 등이 있다. 우선 트랙장비는 기 언급한 공정 중에 PR 도포, Bake, 현상 공정에 사용되는 장비들의 묶음으로서 PR 도포에 사용되는 Spinner(회전의 원심력으로 PR 도포), 베이크 공정에 사용되는 핫플레이트 오븐, 현상공정에 사용되는 Developer 등의 모듈로 구성되어 있다.

리소그래피 공정 장비의 엄청난 시장 규모에도 불구하고 국내 업체들의 매출은 미미한 것이 현실이다. 트랙장비는 한국 DNS, 실리콘테크가 생산 중에 있으며, 고가의 스테퍼는 전부 수입하고 있다. 에처는 기림세미텍, 극동뉴메릭, 아이피에스, 에이티엘, 주성엔지니어링 등의 업체가시제품 내지는 샘플을 제작 생산하고 있는데, 국내 시장 점유율은 아직까지 미미한 실정이며 Asher는 피에스케이테크가 생산하고 있다.

공정상 구분[편집]

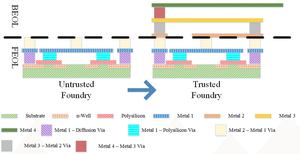

주로 FEOL 과 BEOL 로 구분된다. 다만 만드는 부분에 따라 구분하는 것으로, 실제로 수행되는 공정 자체는 FEOL 이나 BEOL 이나 비슷하다. Photo Lithography, Etching, Deposition, Metallization, Cleaning, Chemical Mechanical Polishing 등.

Front-end of Line (FEOL)[편집]

반도체 칩의 실제 기능을 담당하는 소자(Device)를 형성하는 공정이다. 주로 트랜지스터로 이루어진다. 다음과 같은 부분이 해당된다.

- Isolation (STI 또는 LOCOS)

- Well 형성

- (Transistor 의) Gate 및 Source/Drain

- 기타 Device 에 해당하는 모든 부분

FEOL 공정이 끝나면 소자는 이미 다 형성된 상태가 된다. 그러나 소자끼리, 또는 소자와 패키징 사이가 연결되어 있지 않은 상태이다.

Back-end of Line (BEOL)[편집]

FEOL 에서 만들어진 소자들은 모두 Isolation 되어 있는 상태이다. 이것을 서로 연결하여 신호를 주고받을 수 있게 하는 공정이다. 주로 다음과 같은 부분이 존재한다.

- 소자와 금속 배선 사이의 Contact 형성

- 소자와 소자, 소자와 패키징을 연결하는 금속 배선 형성

- 금속 배선 사이의 절연막 형성

FEOL 공정과 비교하면 큼직큼직하다. 단면도를 보면 소자가 차지하는 부분은 밑바닥에 조금만 있고, 대부분의 부피를 금속 배선이 차지할 정도이다. 그래서 옛날에는 (비교적)쉬운 공정 취급을 받았으나 이제는 작은 크기의 Contact 에서 저항을 최소화하여야 하고, 전체적으로 크기가 작아지면서 금속 배선 자체의 저항도 무시할 수 없어졌으며, 작동중 전류 영향으로 끊어지기도 하고, 배선간 거리가 줄어들어 간섭을 최소화해야 하는 등 난이도가 많이 상승했다.

설계상 구분[편집]

Logic 설계[편집]

웨이퍼에 인쇄할 전자회로(ASIC)의 논리 동작을 설계하는 과정이다. 비선형 동작 외 선형 동작만을 고려하는 단계이다보니 디지털 설계로도 많이 부른다. 동작의 on/off만 고려하면 되기 때문이다.

반도체 설계사들 중 해당 부분만 설계하는 회사를 fabless라고 부른다. IP 설계 회사도 이러한 logic 설계물을 판매하는 회사를 말한다.

여담이지만 제품 기획이나 영업 부분과 자주 만나는 설계부서이기도 하다. 세계적 트렌드에 따라 수요가 있는 제품을 설계하여야 판매로 이어지는 만큼 관련 설계의 최선단에 있는 부서가 미팅에 나갈 수밖에 없기 때문이다.

크게 보면 아래 과정을 순서대로 거친다.

알고리즘 설계[편집]

VHDL/Verilog 언어를 이용하여 algorithm 설계를 진행한다. Algorithm 단계이기 때문에 전압, 전류, 저항 등을 고려하지 않고 clocking time과 delay time에 맞춘 논리 동작의 정합성 여부만 따진다.

논리 검증에는 소프트웨어를 이용하여 시뮬레이션을 진행하는 경우가 많다. 과거에는 논문 등에 적용된 수식을 손수 해석하여 진행했다고 하며, 소프트웨어를 이용하는 지금까지도 아직까지 이 분야에서는 사람이 더 뛰어나기 때문에 석박사가 유독 많은 분야이기도 하다.

그러나 최근에는 대부분의 알고리즘이 시장에 나와있는 만큼 해당 설계 분야의 의의도 변화하고 있다. 이를 디지털 프론트엔드, 디지털 백엔드로 나누어 구분하기도 한다. 디지털 Front-end는 RTL 코드를 만드는 것보다는 이미 작성된 코드를 합성하고, Timing 및 Power 분석을 하고, 회로를 테스트하기 위한 부가적인 기능을 추가하는 DFT(Design For Test)에 관련된 업무를 한다. 디지털 Back-end는 합성된 회로를 배치 및 배선(Place & Route)부터 공정에서 사용되는 마스크(Mask)를 제작하기 전까지의 업무를 진행한다.

Back-end 단의 P&R에 따라서 Front-end에서 했던 Timing 및 Power 분석 결과가 달라지기 때문에 Iteration이 잦아, 사실상 단순 업무 구분 정도의 의미를 지닌다.

회로 설계[편집]

앞서 제작된 algorithm을 회로 형태로 가공하는 과정이다. 이 단계부터는 전압, 전류, 저항, 전자기장, 누설전류 등을 고려한 설계 작업이 진행된다.

대략적인 배선의 기초틀 또한 해당 단계에서 구현되는데, 등가 형태로 구현되는 수준에 그친다. 2차원적 설계에 해당하므로 z축에 대한 부분을 고려하지 않는 것 또한 한계로 꼽힌다.

Layout 설계[편집]

실질적인 도면 설계 과정이다. CAD 프로그램을 이용한 반복 작업이 주가 되며 SoC를 하는 chip maker인 경우에는 wafer에 그려질 도면을, FPGA maker인 경우에는 PCB 기판 도면을 설계하는 과정이다.

반도체 설계사들 중 해당 부분만 설계하는 회사를 design house라고 부른다.

이 단계부터는 layer 구조를 이용하여 z축을 고려할 수 있다보니 3차원적 설계가 진행되며, 회로에서 등가로 표현된 부분을 구현 가능한 형태로 변경하는 작업 또한 진행된다. 덕분에 이 단계에 이르면 전력 소모량, 면적비 같은 가성비 측면도 고려하게 된다.

이 과정에서 구현이 불가능한 logic 설계 부분을 feedback 하는 경우도 있다.

참고자료[편집]

- 〈프론트엔드(반도체)〉, 《나무위키》

- Song 전자공학, 〈Frontend Process & BackEnd Process (전공정과 후공정) / FEOL & BEOL (FrontEnd-Of-Line & BackEnd-Of-Line)〉, 《네이버 블로그》, 2024-07-14

- jhson989, 〈반도체 제조 공정 단계별 정리 (웨이퍼 제조, 프론트엔드, 백엔드 공정)〉, 《티스토리》, 2024-05-11

- 불꽃슛을 꽂아주겠어, 〈반도체 공정 (기초)〉, 《네이버 블로그》, 2017-07-11

같이 보기[편집]

위키원

위키원