반도체 제조

6 µm – 1974

3 µm – 1977

1.5 µm – 1981

1 µm – 1984

800 nm – 1987

600 nm – 1990

350 nm – 1993

250 nm – 1996

180 nm – 1999

130 nm – 2001

90 nm – 2003

65 nm – 2005

45 nm – 2007

32 nm – 2009

22 nm – 2012

14 nm – 2014

10 nm – 2016

7 nm – 2018

5 nm – 2020

3 nm – 2022

미래

2 nm – 2024

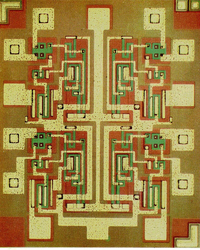

반도체 제조는 전자 소자, 마이크로프로세서, 메모리 칩 등 다양한 반도체 장치를 생산하는 복잡하고 정밀한 공정이다. 이 과정은 첨단 기술과 고도의 정밀성을 요구하며, 반도체는 현대 전자기기의 핵심 부품이다. 반도체 제조는 주로 실리콘 웨이퍼 위에 다양한 미세 회로를 형성하는 일련의 화학적, 물리적 공정을 포함한다.

개요[편집]

반도체 제조 또는 반도체 장치 제조는 일상적인 전기 및 전자 장치에 존재하는 컴퓨터 프로세서, 마이크로 컨트롤러, 메모리 칩(예: NAND 플래시 및 DRAM)과 같은 반도체소자, 일반적으로 집적회로(IC)를 제조하는 데 사용되는 공정이다. 이는 일반적으로 순수한 단결정 반도체로 만들어진 웨이퍼에 전자 회로가 점진적으로 생성되는 다단계 포토리소그래피 및 물리화학적 프로세스(열 산화, 박막 증착, 이온 주입, 에칭 등의 단계 포함)이다. 재료. 실리콘은 거의 항상 사용되지만 특수한 용도로 다양한 화합물 반도체가 사용된다.

제조 공정은 파운드리 또는 "팹"(fab)이라고도 불리는 고도로 전문화된 반도체 제조 공장에서 수행되며 중앙 부분은 "클린룸"이다. 최신 14/10/7nm 노드와 같은 고급 반도체 장치에서는 제조에 최대 15주가 소요될 수 있으며, 업계 평균은 11~13주이다. 첨단 제조 시설에서의 생산은 완전히 자동화되어 밀봉된 질소 환경에서 수행되어 수율(웨이퍼에서 올바르게 작동하는 마이크로칩의 비율)을 향상시키며, 자동화된 자재 처리 시스템은 기계에서 기계로 웨이퍼의 운송을 관리한다. 웨이퍼는 특수 밀봉된 플라스틱 상자인 FOUP 내부로 운송된다. 모든 기계 및 FOUP에는 내부 질소 대기가 포함되어 있다. 가공장비 및 FOUP 내부는 클린룸 내 주변 공기보다 깨끗하게 유지된다. 이러한 내부 분위기를 미니 환경이라고 한다. 제조 공장에서는 지속적으로 질소로 퍼지되는 생산 기계 및 FOUP 내부의 대기를 유지하기 위해 다량의 액체 질소가 필요하다.

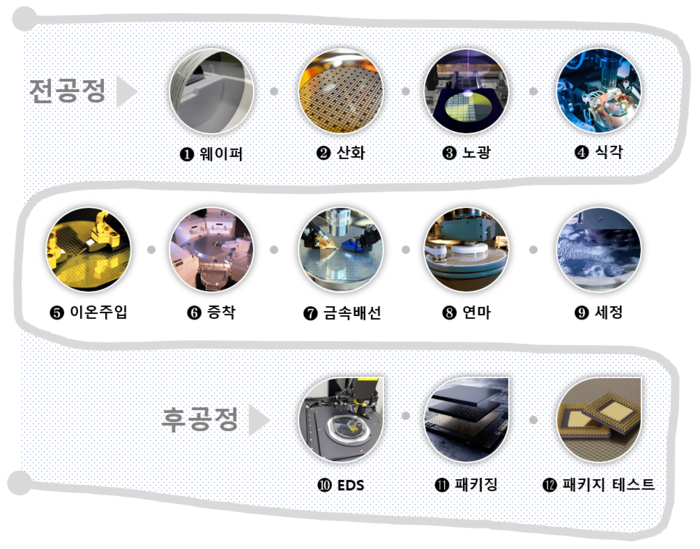

반도체 제조 공정[편집]

반도체 제조 공정은 실리콘 웨이퍼 위에 전자 회로를 형성하는 복잡하고 정밀한 과정이다. 각 단계는 매우 세밀하게 이루어지며, 나노미터 단위의 미세 공정이 요구된다. 주요 제조 공정을 순서대로 설명하면 다음과 같다.

- 1. 웨이퍼 준비

반도체 제조는 실리콘 웨이퍼로 시작된다. 실리콘은 지구상에서 가장 많이 발견되는 원소 중 하나로, 고도로 정제된 실리콘을 사용해 웨이퍼를 제작한다. 웨이퍼는 둥글고 얇은 형태의 실리콘 디스크로, 이후의 공정에서 회로를 집적할 기초 재료이다.

- 2. 산화 (Oxidation)

웨이퍼 표면을 산화시켜 얇은 실리콘 산화막(SiO₂)을 형성한다. 이 산화막은 이후 공정에서 절연체나 보호막 역할을 하며, 웨이퍼의 특정 영역을 보호하기 위해 사용된다.

- 3. 포토리소그래피 (Photolithography)

포토리소그래피는 웨이퍼 표면에 패턴을 인쇄하는 과정이다. 이 과정에서 포토레지스트(photoresist)를 웨이퍼에 도포한 후, 자외선(UV) 또는 극자외선(EUV)을 사용해 마스크에 있는 회로 패턴을 웨이퍼 위에 전사한다.

- 포토레지스트 도포: 웨이퍼에 감광성 물질인 포토레지스트(photoresist)를 얇게 도포한다.

- 노광 (Exposure): 빛을 이용해 마스크(회로 패턴이 새겨진 판)를 통해 포토레지스트를 노광한다. UV(자외선) 또는 EUV(극자외선) 리소그래피가 사용된다.

- 현상: 노광된 부분과 노광되지 않은 부분이 현상액을 통해 제거된다. 이렇게 형성된 패턴은 다음 단계에서 이온 주입이나 에칭 작업의 가이드 역할을 한다.

- 4. 이온 주입 (Ion Implantation)

이온 주입은 불순물을 웨이퍼에 주입해 전기적 특성을 조정하는 과정이다. 이를 통해 반도체소자의 도핑 영역을 형성하며, 트랜지스터 등의 전기적 특성을 제어한다. 이 공정을 통해 웨이퍼의 도핑(doping) 영역을 형성하며, 트랜지스터와 같은 소자의 기능을 결정한다.

- 5. 에칭 (Etching)

에칭은 포토리소그래피로 형성된 패턴에 따라 불필요한 물질을 제거하는 과정이다. 화학적 또는 물리적 방법을 사용해 웨이퍼의 불필요한 부분을 제거해 패턴을 형성한다.

- 습식 에칭: 화학약품을 사용해 물질을 녹여내는 방식.

- 건식 에칭: 플라즈마 등을 이용해 물질을 기계적으로 제거하는 방식으로, 미세한 패턴 구현에 유리하다.

- 6. 증착 (Deposition)

증착은 웨이퍼 표면에 새로운 물질을 증착하는 과정이다. 화학 기상 증착(CVD)과 물리 기상 증착(PVD) 방식을 사용해 박막을 형성한다.

- 화학 기상 증착(CVD): 가스 상태의 물질을 웨이퍼에 반응시켜 박막을 형성하는 방식.

- 물리 기상 증착(PVD): 증착할 물질을 기화시켜 웨이퍼에 물리적으로 부착시키는 방식.

- 7. 연마 (CMP, Chemical Mechanical Planarization)

연마는 증착 후 고르지 않은 웨이퍼 표면을 평탄하게 만드는 과정이다. 이를 통해 웨이퍼 표면을 균일하게 만들어 다음 공정이 정밀하게 이루어지도록 한다.

- 8. 메탈화 (Metallization)

반도체소자 내의 회로를 연결하기 위해 금속을 웨이퍼 표면에 증착하는 과정이다. 알루미늄이나 구리 같은 금속이 사용되며, 전기적 신호가 반도체 칩 내외로 원활하게 흐를 수 있도록 한다.

- 9. 패키징

완성된 반도체 칩을 외부 충격과 환경으로부터 보호하기 위해 패키징 공정이 이루어진다. 패키징은 또한 칩을 전자기기와 연결하는 역할을 하며, 소형화된 회로가 안정적으로 작동할 수 있도록 보호한다.

이러한 반도체 제조 공정은 나노미터(1nm=10⁻⁹m) 단위의 매우 미세한 작업을 필요로 하며, 최신 기술인 극자외선(EUV) 리소그래피나 미세 공정(7nm, 5nm) 등이 도입되고 있다. 주요 반도체 제조 기업인 삼성전자, TSMC, 인텔 등은 이러한 첨단 기술을 바탕으로 글로벌 시장을 선도하고 있다.

이 공정들은 고도의 기술력을 요구하며, 수십 개의 단계를 거쳐야 하므로 시간이 오래 걸리고 비용도 많이 소요된다.

주요 기술적 이슈[편집]

- 미세화 공정: 트랜지스터 크기가 점점 작아지면서 미세화 공정의 난이도가 크게 증가하고 있다. 현재 5nm 이하의 초미세 공정이 상용화되었으며, 3nm 공정도 연구 중이다.

- EUV 리소그래피: 극자외선(EUV) 리소그래피는 7nm 이하의 미세 공정을 실현하는 데 중요한 역할을 하고 있으며, 첨단 반도체 제조에 필수적이다.

- 재료 혁신: 실리콘 외에도 GaN(갈륨 나이트라이드), SiC(실리콘 카바이드)와 같은 새로운 반도체 재료가 연구 및 사용되고 있다. 이들은 고효율, 고온, 고전압 환경에서 뛰어난 성능을 발휘한다.

반도체 제조의 주요 기업[편집]

- TSMC (Taiwan Semiconductor Manufacturing Company): 세계 최대의 파운드리(반도체 위탁생산) 기업으로, 전 세계적인 반도체 공급망의 중심에 있다.

- 삼성전자: 메모리 반도체뿐만 아니라 비메모리 반도체 시장에서도 중요한 역할을 하며, 최첨단 미세 공정 기술을 보유하고 있다.

- 인텔: CPU 및 다양한 반도체 제품을 생산하는 세계적인 기업으로, 반도체 공정 기술 혁신을 주도하고 있다.

참고자료[편집]

같이 보기[편집]

위키원

위키원