범프

범프(Bump)는 칩을 기판에 TAB, FC방식으로 연결하거나 BGA, CSP등을 회로기판에 직접 접속하기 위한 전도성 돌기를 말한다. 범프의 역할은 플립칩(Flip Chip)이 용이 하도록 전극의 높이를 높이는 역할을 하고, 전극재료를 외부전극과 접속이 용이한 재료로 교체하는 역할을 한다.

Solder Bump의 경우 Reflow 공정 후 표면장력효과에 의하여 Ball 모양이 형성되지만, Au Bump의 경우 도금 형태인 사각기둥 모양을 유지한다.

Bump의 재료로는 Au, Solder, Cu등의 금속재료와 수지에 금속입자가 혼입된 도전성 수지 또는 수지표면에 금속재료를 피복한 수지-금속복합재료로 구별된다.

개요[편집]

범프는 반도체 패키징에서 칩과 기판 간의 전기적 연결을 형성하기 위해 칩 표면에 형성된 작은 금속 돌기이다. 범프는 전도성을 가지며, 칩과 외부 회로 기판 사이의 전기 신호 전달과 열 관리, 기계적 지지 등을 돕는다. 일반적으로 금, 주석, 구리 등의 금속으로 만들어지며, 다양한 패키징 기술에서 중요한 역할을 한다.

범프의 종류[편집]

- 솔더 범프 (Solder Bump): 주석과 납 등의 솔더 합금으로 만들어지며, 리플로우 공정을 통해 부착됩니다. 플립칩 패키지에서 널리 사용된다.

- 구리 범프 (Copper Bump): 구리를 사용하여 만들어지며, 높은 전기적 전도성과 내구성을 가지고 있다. 고밀도 및 고성능 패키지에 적합하다.

- 금 범프 (Gold Bump): 금을 사용하여 형성되며, 저항이 낮고 전기적 성능이 우수하여 와이어 본딩 및 아날로그 소자에 자주 사용된다.

- 압력 접촉 범프 (Pressure Contact Bump): 납땜 없이 기판에 압력을 가해 결합되는 범프 형태로, 재작업이 가능한 패키징에 주로 사용된다.

범핑공정[편집]

범핑(Bumping)공정은 반도체 packaging과 assembly 과정에서 반도체 칩(Die)과 기판(Substrate) 단자 사이에 전기적 연결을 확보하는 배선(Wiring) 공정에서 기존의 와이어 본딩(Wire Bonding)이 아닌 돌기(bump) 모양의 금속을 형성해 연결하는 반도체 후공정의 일부이다.

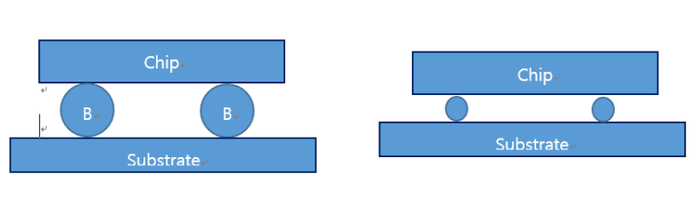

일반적인 반도체 패키지에서 상부 구조인 칩과 기판을 연결하는 방식은 크게 2가지 1) Wire Bonding 방식을 보면 칩 단자와 기판(Substrate)을 미세한 금선(gold wire)으로 연결 2) Bumping 방식에서는 반도체 칩 위에 직접 돌기 형태의 Bump를 만들어 기판과 전기적으로 연결

이 때 Bumping 방식이 적용된 칩을 플립칩(Flip Chip)이라고 하는데, 반도체 칩을 기판에 부착할 때 금속 와이어와 같은 추가적인 연결 구조를 사용하지 않고 칩을 뒤집어 (flip의 사전적 의미가 '뒤집다'이다) 칩 아랫면의 (active area) 전극 패턴을 이용해 그대로 융착, 기판과 연결되기 때문이다. 즉 flip chip bonding이 bump를 이용해 연결하기 때문에 이 둘을 혼용해서 사용하기도 한다.

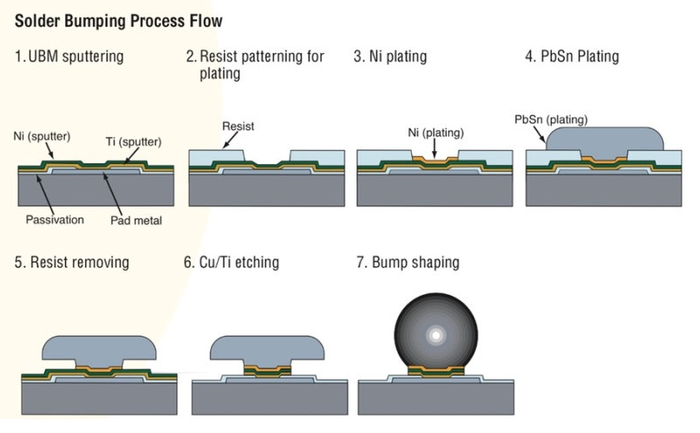

가장 일반적인 웨이퍼 범핑 공정은 아래 그림과 같은데 (Pb-Sn solder bump 기준임)

- 1)UBM sputtering

전공정이 끝난 팹 아웃 (fab out) 웨이퍼에 스퍼터링 (그림에서는 스퍼터링 방식을 이용한 것이고 진공 증착 / 전기 도금 등의 방법도 이용)을 통해 UBM (Under bump metallization) 증착을 한

UBM (Under bump metallization): 건물로 치자면 기초 공사에 해당할 만큼 중요한 공정으로 증착이 끝난 metal이라고 생각하면 된다.

반도체 칩의 Ai나 Cu 전극에 직접 범프를 형성하기가 어렵기 때문에 접착이 용이하도록 전극과 범프 사이에 이 UBM이 기초 골조처럼 들어가는 것이다.

접합층 + 확산방지층 + wettable 층의 3가지 layer로 구성

- 2)Resist patterning for plating

PR (포토 레지스트) 패턴을 형성한 뒤

- 3) Ni plating & PbSn plating

도금액을 이용해 차례로 Ni, PnSn 도금막을 형성함

- 4) Resist removing 및 Cu/Ti etching

이후에 식각 공정으로 포토 레지스트 등을 제거하면 UBM 층 위에 솔더볼, 솔더 페이스트, 구리기둥 (Copper pillar) 등 범프가 형성

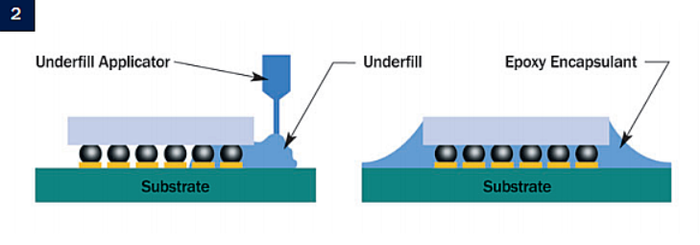

- 5) 언더 도포 (underfill) 및 경화 공정을 거치게 됨

마지막으로 반도체 칩과 기판 사이 attach되어 있는 bump를 보호하기 위해 범프 사이 사이를 채워주는 공정

특히 이 under fill 공정은 EMC (epoxy molding compound)가 채우기 어려운 범프와 범프 사이 사이를 메꿔줌으로써 package의 신뢰성을 확보해주고 칩의 열방출을 극대화 시키게 된다. 한데 이 under fill 공정의 치명적인 단점은 한 번 도포가 끝나버리면 repair가 불가능하다는 점이다.

최근에는 별도의 under fill 공정 없이 molding 같은 범용 기술을 이용해서 미세 silica 입자로 구성된 EMC 재료를 사용해 범프와 범프 사이를 molding 시에 한 번에 채워주는 MUF (Moldedunder fill) 공법을 많이 이용하고 있다.

소재에 따른 bumping 방식 구분[편집]

가장 일반적으로 사용되는 solder (우리가 흔히 말하는 납땜) bump 이외에도 용도에 따라 금(Au), 구리, 또는 코발트 등도 사용할 수가 있다. 구리 기둥은 최근에 고밀도 연결 또는 미세한 피치가 요구되는 어플리케이션에서 주로 적용 중이다.

- ▶ Gold (Au) bumping

주로 비메모리 그 중에서 디스플레이 패널에 사용되는 DDI (Display Driver IC) 에 한정되어 적용 중, 다만 디스플레이 패널 시장이 TV, Mobile 모두 성장하고 있으므로 수요도 지속적으로 증가될 전망이다.

2018년 기준 AMOLED 시장은 출하량 기준 8.6% 성장, 2019년은 14.2%의 고성장이 예상되나. 2020~2023년까지 CAGR 10.4%의 두자릿수 성장 예상 중이다. 글로벌 하게는 대만의 Chipbond와 ChipMOS Technologies가 DDI를 위한 Au bumping 시장의 2/3를 차지하고 있다.

국내에서는 DDI bumping은 네패스와 엘비세미콘이 주요 업체이고

- - 네패스는 삼성전자 비중이 절대적으로 높고

- - 엘비세미콘은 실리콘웍스 (--> LG디스플레이) 향 매출에 크게 의존적이었으나 2018년 2분기부터 삼성전자향 매출이 증가하기 시작 (2018년 2 분기 8%→3 분기 14%→4분기 20%→ 2019년 1분기 21%) 등 분기를 거듭할수록 증가하였다.

Au bumping은 이름 그대로 주요 원재료가 Au이기 때문에 국제 금시세에 연동이 된다.

- ▶ Solder bumping

PMIC, CIS, AF-IC, RF-ID 등 적용 가능한 디바이스가 gold bumping에 비해 다양하고 시장 성장률도 더 높을 것으로 예상된다. 특히 요즘은 CIS (Camera Image Sensor) 패키지에 주로 적용되어 수요 증가 중이다.

- - 초기에는 lead 즉 납을 이용한 solder가 주로 사용되었고 현재도 Tin-lead eutectic solder (Sn�Pb eutectic solder)가 사용 중이다.

- - 하지만 이 납... 언제나 이슈가 되는게 납은 환경 문제나 인체 유해? 이런 문제들이 따라다니다 보니 이제는 Pb-free solder가 많이 사용된다. (Lead free라고 LF라고도 함)

이러한 범프를 이용한 flip chip bonding 방식은 기존의 wire bonding 방식에 비해

- 칩과 기판간의 접속부 길이가 최소화 되어 전기적 성능이 우수

- 입출력 단자의 집적도를 높일 수 있음

- 열 방출 경로를 분산시켜 내부의 열을 보다 빠르게 외부로 방출

최근에는 TSV, Fan-out packaging 등 새로운 기술의 적용으로 bump의 size도 더욱 미세화 되는 추세이고 이로 인해 fine pitch bump 기술력이 경쟁력이라고 할 수 있다. 여기서 골칫거리는 선폭이 더욱 더 미세화 되면서 여러 문제들이 발생하는 점이다.

선폭 미세화 --> 칩 면적의 감소 & 대신 기능은 더욱 많아져서 I/O 단자 수는 더욱 증가

- --> 단자 간의 거리가 감소

- --> 자연스럽게 solder bump의 크기도 감소: fine solder ball pitch와 small ball attach 기술이 발전

문제는 이러한 미세 solder bump를 사용하게 되면서

- 칩과 기판 거리가 너무 감소하다 보니 underfill 공정에 난이도가 올라가는 문제가 발생

- solder bump의 크기가 감소하면서 범프 접속부에 전류 밀도와 열에너지 밀도가 증가하게 됨

그래서 이러한 솔더범프를 사용한 플립칩 공정의 문제점을 해결하기 위해 나온 방법이

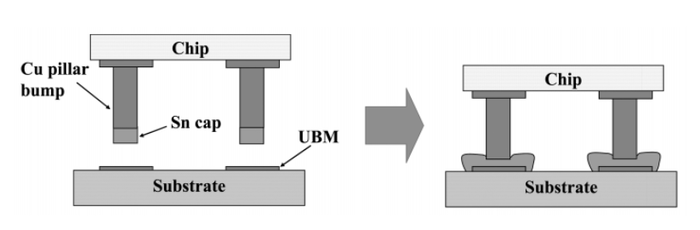

- ▶ Copper pillar (구리기둥) bumping (CPB)

- Fujitsu의 CSP 패키징에 최초로 도입된 이후 2010년 Texas instrument와 Amkor에 의해 Copper pillar flip chip packaging 기술이 발표된다.

위 도식도를 보면... I/O 단자 간격이 좁아진 초 미세 피치일 경우 혹시 모를 간섭을 방지하기 위해 I/O 단자마다 우선 Cu pillar 즉 구리 기둥을 세우게 되고 Sn cap 즉 솔더 캡을 씌워주게 됨 (전기 도금). 이후에 칩을 기판 위에 올리고 열처리 장비에 넣으면 솔더가 녹으면서 기판 위 UBM에 붙게(bonding) 되는 원리이다.

Cu pillar bumping 방식은 이 구리 기둥 덕분에 칩과 기판 사이의 거리가 감소하지 않으면서도 훨씬 미세한 칩 접속이 가능한 게 가장 큰 장점이다. 이전에 쓰던 solder bump는 대응 가능한 최소 pitch가 75um 이상인데 반해 Cu pillar bumping은 fine pitch (40um 이하의 미세 피치의 고밀도 패키지 구현이 가능함)

또하나 RF 패키지의 경우에는 사용 주파수가 높아서 칩과 기판 사이 거리가 짧아지면 기생 커패시턴스가 증가해 패키지 성능이 현저히 저하되는 근본적인 문제점이 있다.

하지만 Cu pillar bump는 칩과 기판 사이 거리가 확보되므로 이러한 문제로부터 자유롭다.

이 Cu pillar bumping은 주로 RFIC나 Baseband, AP, PMIC 등의 어플리케이션용 인터커넥트에 적합하고 이러한 장점을 바탕으로 CPB 기술은 급격히 성장, 2010년 기준 플립칩 인터커넥트 시장의 25%를 차지하던 것이 2015년에 50% 이상, 2018년말 약 75%까지 차지하고 있다.

한데 이 마저도 10nm 이하 칩에서는 활용이 어려워 지는데 단순히 열처리만을 이용하면 Cu pillar (구리 기둥)이 휘어버리는 문제가 발생하기 때문이다. 그래서 또 이를 해결하기 위한 대안이 TC 방식 (Thermal compression)의 공정이다. 기존 공정은 단순히 압착없이 칩을 기판 위에 올리고 열처리 장비에 넣어서 붙이기만 했다면 TC방식 공정은 칩과 기판 사이에 전기가 통하는 전도성 페이스트나 필름을 넣고서 칩을 압착하고 열을 가해 접합하는 방식이다.

참고자료[편집]

- investment/candidate, 〈:: Flip Chip이란? Bump란 무엇인가?〉, 《티스토리》, 2011-02-12

- Ging Ging, 〈Bumping 공정〉, 《네이버 블로그》, 2019-12-18

같이 보기[편집]

위키원

위키원