절연막

절연막(絶緣膜, Insulator film)은 집적 회로(IC)를 제작하는 웨이퍼 프로세스 기술에 쓰이는 비도전성의 막을 말한다.

목차

개요

절연막은 전기적 절연 특성을 가진 얇은 층으로, 반도체 소자나 전자 장치의 부품 사이에 전기적 간섭을 방지하고, 특정 부분의 전기적 특성을 제어하는 데 사용된다. 절연막은 높은 저항과 유전 상수를 가지며, 소자 내 전류 누설을 방지하고, 열적 안정성, 화학적 안정성을 제공한다. 주로 산화막과 질화막이 많이 사용되며, 유리, 폴리머, 사파이어 등의 소재도 절연막으로 활용된다.

주요 절연막 유형과 특성

산화막 (Oxide Layer)

- 실리콘 산화물(SiO₂): 가장 널리 사용되는 절연막이며, 높은 절연성과 안정성을 제공한다. 트랜지스터의 게이트 산화막과 웨이퍼 표면의 보호층으로 많이 사용된다.

- 유리(Silicate Glass): 고온에서 용해가 쉽고 다양한 용도로 적용 가능한 절연재로, 소자의 보호층과 패시베이션 층으로 사용된다.

질화막 (Nitride Layer)

- 실리콘 질화물(Si₃N₄): 높은 절연성과 기계적 강도를 가지며, 확산 방지막과 패시베이션 층으로 자주 사용된다. 산화막에 비해 물리적 강도가 뛰어나며, 습기와 산소에 대한 내성이 높다.

- 질화 갈륨(GaN): 고출력 및 고주파 소자에 사용되며, 뛰어난 전자 이동성과 고온 안정성을 제공한다.

유기 절연막 (Organic Insulating Layer)

- 폴리이미드(Polyimide): 유연성이 뛰어나고 고온에서도 안정적이며, 주로 플렉서블 전자기기에서 절연층으로 사용된다.

- 에폭시(Polymer Epoxy): 경화 후 단단하게 굳어져 소자의 보호층과 절연층으로 사용된다.

고유전율 절연막 (High-k Insulator)

- 하프늄 산화물(HfO₂): 높은 유전율로 인해 소형화된 반도체 소자의 게이트 산화막으로 사용되며, 낮은 누설 전류와 높은 절연성을 제공한다.

- 탄탈 산화물(Ta₂O₅): 높은 유전 상수와 안정성을 가지고 있어, 고밀도 DRAM 및 트랜지스터의 게이트 절연층으로 사용된다.

사용 방법

반도체 칩에서 절연막은 크게 3가지 종류로 쓰인다.

- 1) Trench Isolation

반도체칩은 수많은 Transistor 소자들로 구성되어 있다. 그런데 이웃하는 Transistor들이 서로 간섭을 하면 안된다. 그래서 Transistor들을 서로 분리해주기 위해 트렌치 (Trench)를 판다.

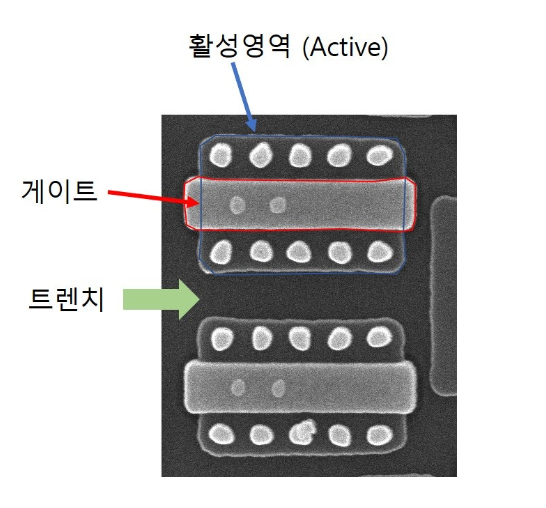

반도체를 수평면에서 보면 아래와 같이 생겨 있다. Transistor 채널이 생기는 활성영역 (Active), 그리고 활성영역 위에 올라가는 게이트. 물론 콘택도 있다. 활성영역들을 자세히 보면 섬같이 분리가 되어 있는 구조다. 이웃하는 활성영역이 트렌치에 의해서 분리가 되어 있다.

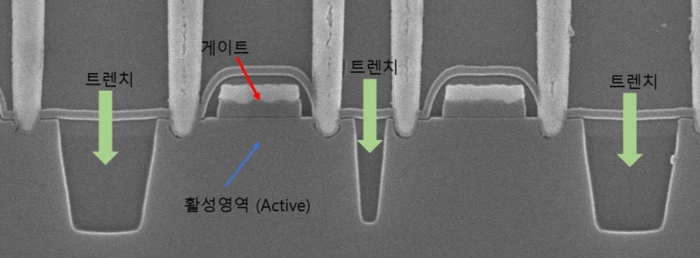

이 트렌치는 깊이 2000~5000A 정도의 구덩이 이다. 밑으로 쑥 꺼져 있는셈이다. 수직단면으로 보면 이렇게 생겼다.

이 트렌치는 Transistor 소자들을 분리하는 목적이다. 즉 이웃하는 Transisitor를 전기적으로 분리한다. 그럼 이 트렌치를 그냥 비워둘까? 아니다. 이 트렌치 안에는 실리콘 절연막 (SiO2)을 꽉 채워준다. SiO2 가 절연물질로 절연의 역활을 하는것이다. 사실 실리콘 절연막 (SiO2) 는 유리와 거의 비슷한 물질로 보면 된다. 형성하는 방법이 달라서 그렇지 물질 자체는 거의 유사하다.

이 트렌치 공정에서 중요한 부분은 절연물질의 Gap fill 능력이다. 즉 트렌치 안에 절연물질을 빈 공간없이 잘 채워야한다. 물론 소자간 전기적으로 분리를 위해 절연물질의 유전율도 낮아야 겠지만 최근은 제품 미세화로 트렌치의 폭이 작아져 이 좁은 트렌치 안에 어떻게 하면 절연막을 잘 채울지가 중요한 부분이다. 그래서 보통 undoped silicate glass라는 floawable 한 USG 막질이 주로 사용되었으며 최근에는 더 물같이 잘 흘러들어가 증착되는 TOSZ(Tonen SilaZene) 같은 물질도 개발되어 적용하고 있다.

- 2) ILD(Inter Layer Dielectric)

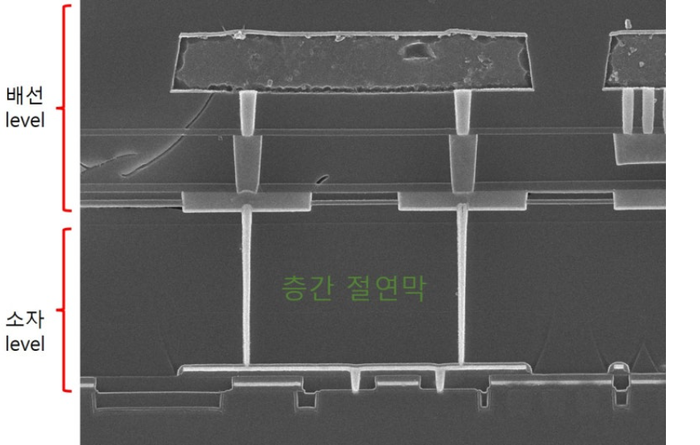

반도체는 모두 층으로 이루어진 구조라고 했다. 반도체 물질 한 층 증착해서 포토공정 후 깍아내고 그 위에 다시 다른 물질층 한층 올리고 다시 깍아내고...이런 공정들을 반복해서 반도체 칩을 만든다. 그럼 ILD (Inter Layer Dielectric)는 뭘까? 예를 들어 게이트 다 만들고 나서 게이트를 덮어주는 물질이 필요하다. 이게 층간 절연막 ILD이다. ILD 층은 보통 소자 즉, Transistor 를 만들어주고 그 위를 덮어주는데 이 ILD 층위로는 배선 공정이 시작되기 때문에 무엇보다도 평탄하게 증착이 되어야 한다. 물론 요즘은 증착후 CMP 같은 공정으로 평탄화를 하는게 일반적이긴 하다. 그래서 소자와 배선사이에 절연을 해주는 목적으로 증착된다.

사용되는 막질은 Boron and Phosphorus doped silicon oxide films 인 BPSG와 Tetraethylorthosilicate인 TEOS 가 사용된다. 이 ILD 역시 Gap fill 능력이 좋아야 하기때문에 Flowable한 물질을 사용하는 추세이다.

- 3) IMD(Inter Metal Dielectric)

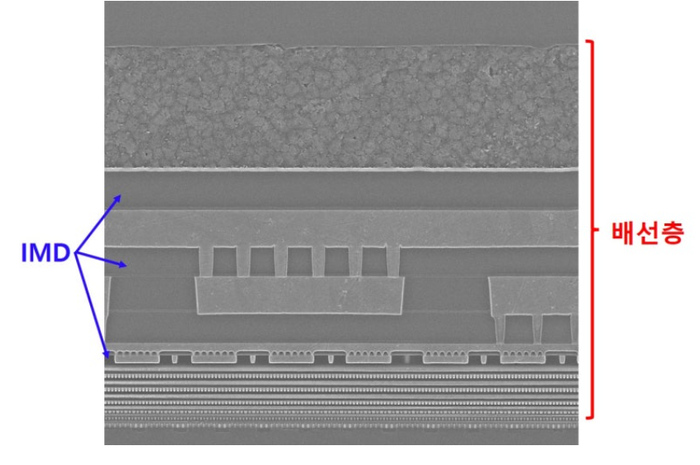

자 이제 배선층으로 가보자. 아래 그림처럼 반도체 칩에서 배선층의 비중은 거의 90% 이상이다.

칩사이즈가 더 작아질수록 반도체 칩이 메세화가 될수록 배선층의 수는 증가하고 배선들의 사이즈는 줄어든다. 보통 메모리는 4~5개 층의 배선층을 사용하고 AP, CPU 같이 연산용 반도체 칩은 배선층이 10개 층이 훨씬 넘어가고 있다.

IMD(Inter Metal Dielectric). 말 그대로 메탈사이에 들어가는 절연막질이다. 여기서 말하는 메탈은 배선층이다. 배선층을 절연할때 가장 중요한건 유전율이다. 유전율은 간단하게 이야기 하면 배선과 배선사이에 절연막이 들어가는데 절연막 종류에 따라 배선에 흐르는 전기가 이웃하는 배선에 영향을 주는 인자다. 유전율이 낮아야 옆에 배선에 영향을 덜준다.

결론은 반도체 칩내 배선은 상상이상으로 가까이 붙어 있는 상황이라 배선끼리 절연을 하더라도 전기적인 영향을 주고 있으며 따라서 절연막질의 유전율이 매우 매우 중요하다. 그럼 저렇게 조밀한 배선들 사이에 절연막이 들어가야 하는데 유전율만큼 Gap fill 능력이 중요하다. 그런데 중요한 시기가 있었고 지금은 배선 형성하는데 있어 절연막을 Gap fill 하지 않는 공정을 주로 사용하고 있어 유전율이 더 중요한 상황이다.

IMD 막질은 말한것처럼 유전율이 매우 중요하기 때문에 최근에는 Ultra Low-K 라고 불리는 막질이 사용된다. 간단히 Ultra Low-K 는 절연막내 빈 공간을 수없이 형성하여 절연막의 유전율을 낮춘 개념이다. 즉 Air Gap 개념이다.

참고자료

- 〈절연막〉, 《전자용어사전》

- 릴츠, 〈반도체 겉핥기 21 : 반도체 절연막에 대해〉, 《네이버 블로그》, 2022-06-02

같이 보기

위키원

위키원