소자분리

소자분리(Device Isolation)는 각 소자들 사이에서 일어나는 상호작용(전류 이동 등)을 막기 위해서 각 소자간의 영역을 분리하는 것을 말한다.

목차

개요[편집]

소자분리는 반도체 제조 공정에서 각 소자(트랜지스터, 다이오드 등)가 전기적으로 독립되도록 하는 기술이다. 소자분리는 서로 인접한 소자 간의 전기적 간섭을 최소화하여 각각의 소자가 독립적으로 동작할 수 있도록 한다. 이는 집적회로(IC)의 안정성과 성능을 보장하기 위한 필수적인 단계이다.

소자분리는 집적회로 내에서 개별 소자 간의 누설 전류를 방지하고, 소자 간의 간섭을 줄여 신호의 정확성과 신뢰성을 높이기 위해 수행된다. 소자 간의 전기적 분리를 통해 각 소자가 독립적으로 동작하도록 하여 전체 회로의 성능을 극대화할 수 있다.

소자분리 방법[편집]

LOCOS(Localized Oxidation of Silicon)[편집]

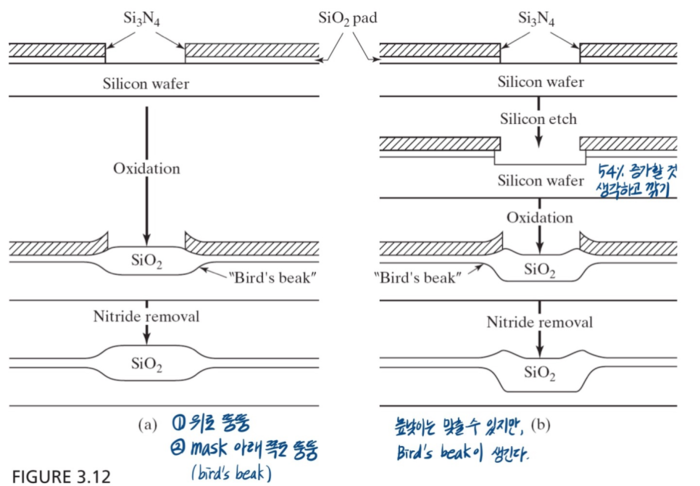

기존에 사용되던 소자 격리 기술로 반도체 기판 상에 산화막을 선택적으로 성장시켜 소자분리막을 형성한다.

Semirecessed structure과 Fully recessed structure로 나뉘는데, fully recessed는 semirecessed보다 bird's beak이 적게 생기지만 결론적으로 두 공정 다 bird's beak이 발생하므로 요즘은 LOCOS 방식을 사용하지 않는다. (bird's beak 현상에 의해 pad oxide가 active region까지 침투한다.)

Deep Trench Isolation[편집]

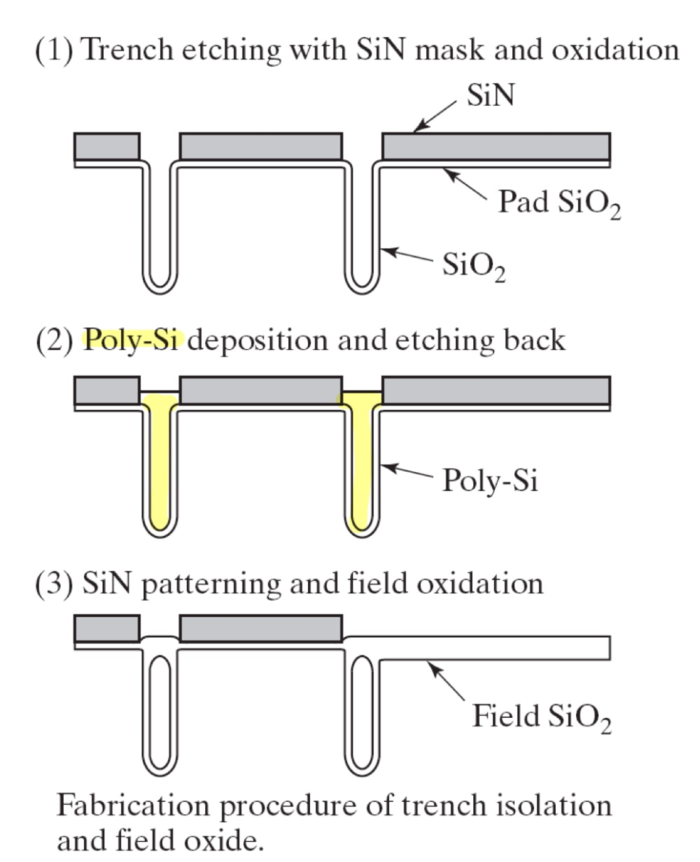

주로 DRAMS에서 사용되는 방식으로, 얇고 깊게 식각해서 밀도가 높은 벽을 만들 수 있다. (만들기 어렵다)

STI(Shallow Trench Isolation)[편집]

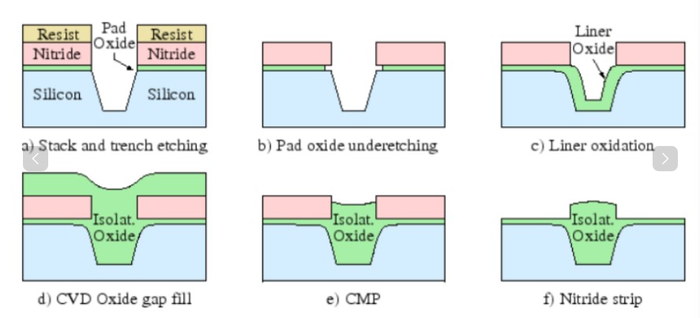

소자간의 분리와 device capacitance를 최소화하기 위해 사용하는 방법으로, deep trench보다 간단하다.

STI는 웨이퍼 표면에 얕은 트렌치를 형성하고 이를 산화막으로 채워서 소자 간 절연을 제공한다. LOCOS에 비해 공간을 효율적으로 사용할 수 있어, 고집적 회로에서 널리 사용된다. 공정 과정에서 트렌치 식각, 절연 물질 충진, 평탄화 등의 단계를 거친다. LOCOS에 비해 트랜지스터 사이의 거리를 줄일 수 있어, 집적도가 높은 반도체 소자 제작에 유리하다.

SOI(Silicon on Insulator)[편집]

SOI는 절연층 위에 얇은 실리콘 층을 형성하여 트랜지스터와 같은 소자를 형성하는 방식이다. 절연층(Silicon Dioxide)이 소자 전체 아래에 위치해 전기적 간섭을 최소화하며, 각 소자가 독립적으로 동작할 수 있도록 돕는다. 누설 전류 감소, 속도 향상, 소비 전력 절감 등의 장점이 있어 고성능 저전력 소자에 적합하다.

Field Isolation Techniques[편집]

필드 산화막(Field Oxide Layer)을 이용하여 소자 간 전기적 분리를 제공한다. 소자 주위에 필드 산화막을 형성하여 주변 소자와의 전기적 간섭을 줄이고, 원하는 영역에서의 전류 흐름을 제한한다.

필드산화막 형성과 트랜치 형성이 혼합된 소자 격리방법에 관한 것으로서, 설계 규칙이 0.25㎛ 또는 그 이하가 되는 소자 제조기술에서 사용될 소자 격리 방법에 관한 것이다. 본 발명은 종래 기술에서 트랜치를 사용한 구조에서의 문제가 될 수 있는 폭이 넓이 영역의 트랜치 형성 및 채우기를 해결하기 위해, 실리콘 기판 위에 열산화막을 성장시키고, 제1질화막을 증착하고 산화질화막을 형성하고, 그 위에 제2질화막을 증착하고, 활성영역을 형성하기 위해 사진식각 공정을 거쳐 건식식각하는 제1공정과, 산화막을 증착하고 그 산화막을 과도비등방성 건식식각하여 산화막 스페이서를 형성하는 제2공정과, 얇은 열산화막을 성장하고 질화막을 덮고 비등방성 건식식각하여 질화막 스페이서를 형성하는 제3공정과, 제1필드산화막을 성장하고 제2질화막과 질화막 페이서를 습식식각하는 제4공정과, 실리콘 기판을 파서 트랜치를 형성하고 얇은 열산화막을 성장하고 CVD 법으로 산화막을 증착하는 제5공정과, 증착된 산화막을 등방섕 건식 또는 비등방성 습식하는 제6공정과, 두께가 상대적으로 작은 미니 필드산화막을 성장하는 제7공정으로 이루어진 것이다.

전사과정 소자분리[편집]

- 스티커 방식 소자분리

2024년 6월 25일, 김대형 기초과학연구원(IBS) 나노입자 연구단 부연구단장과 부산대 연구진은 전자 소자를 기판에서 손상 없이 분리할 수 있는 새로운 전사 기술을 개발했다고 발표했다. 이 기술은 기존보다 전사에 필요한 시간과 비용을 크게 절감하여, 고성능 전자기기 제작에 폭넓게 활용될 것으로 기대된다.

전사 공정이란 반도체 제작 시 기판에서 소자를 떼어내어 이동시키는 과정이다. 최근에는 고온에서 안정적인 단단한 기판 위에 고성능 소자를 제작하고 이를 유연한 기판으로 옮겨 플렉서블 장치 제작에 활용하는 경우도 늘고 있다.

기존 전사 공정은 기판과 소자 사이에 위치한 '희생층'을 화학적으로 제거하는 방식으로 진행된다. 그러나 이러한 화학물질은 작업자의 건강에 유해할 수 있으며, 소자에 화학적 손상을 초래할 위험이 있다. 물이나 레이저를 이용하는 새로운 방법들도 개발되었으나, 이러한 방법은 고가의 장비가 필요하고 추가적인 처리 과정이 필요한 단점이 있다.

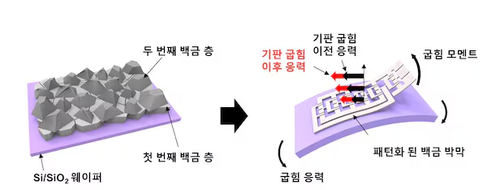

IBS 연구진은 기판 특성을 제어하여 소자를 손상 없이 떼어내는 '무손상 건식 전사' 기술을 개발하여 이러한 문제를 해결했다. 이 기술은 물리적 힘을 이용해 소자를 쉽게 분리할 수 있도록 하는 특수 기판 소재를 적용한 것이다.

이 기판은 서로 다른 응력을 가진 두 층의 박막으로 이루어져 있다. 외부에서 힘을 가했을 때 변형률의 차이로 인해 발생하는 변형 에너지가 기판과 소자 사이의 결합보다 클 경우, 소자는 기판에서 쉽게 떨어진다.

연구진은 이 새 기판 위에서 소자를 제작한 후, 기판을 구부려 소자를 떼어내는 방식을 개발했다. 이렇게 떼어낸 소자는 원하는 기판에 손쉽게 옮겨 붙일 수 있다.

참고자료[편집]

- 공대(인)생, 〈isolation 공정: STI (Shallow Trench Isolation) - 공대(인)생〉, 《티스토리》, 2023-07-07

- 식식피그, 〈삼성전자의 CIS 기술 - 아이소셀(ISOCELL) -> Deep Trench Isolation (DTI 공정)〉, 《티스토리》, 2021-07-29

- admgenie, 〈필드산화막 형성과 트랜치 형성이 혼합된 소자격리방법 (Isolation Method Mixing Forming Field Oxide Film And Forming Trench)〉, 《서울대학교 이종호 교수님 연구실》, 2024-03-25

- 박우엉, 〈<CMOS 반도체 공정> STI를 이용한 소자간 영역 분리〉, 《네이버 블로그》, 2022-03-12

- 이병철 기자, 〈스티커 떼어내듯 기판서 반도체 소자 분리…“공정 비용 대폭 절감”〉, 《조선비즈》, 2024-06-25

- 신선미 기자, 〈반도체 소자 분리기술로 `STI 공정` 각광〉, 《전자신문》, 2006-02-24

같이 보기[편집]

위키원

위키원